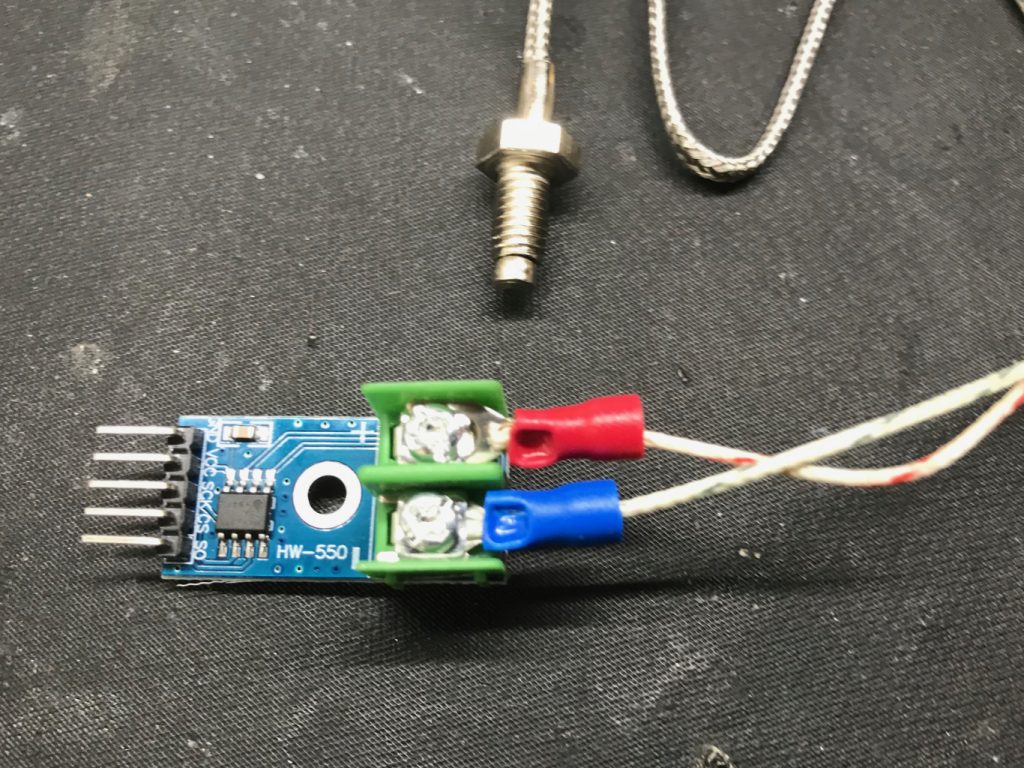

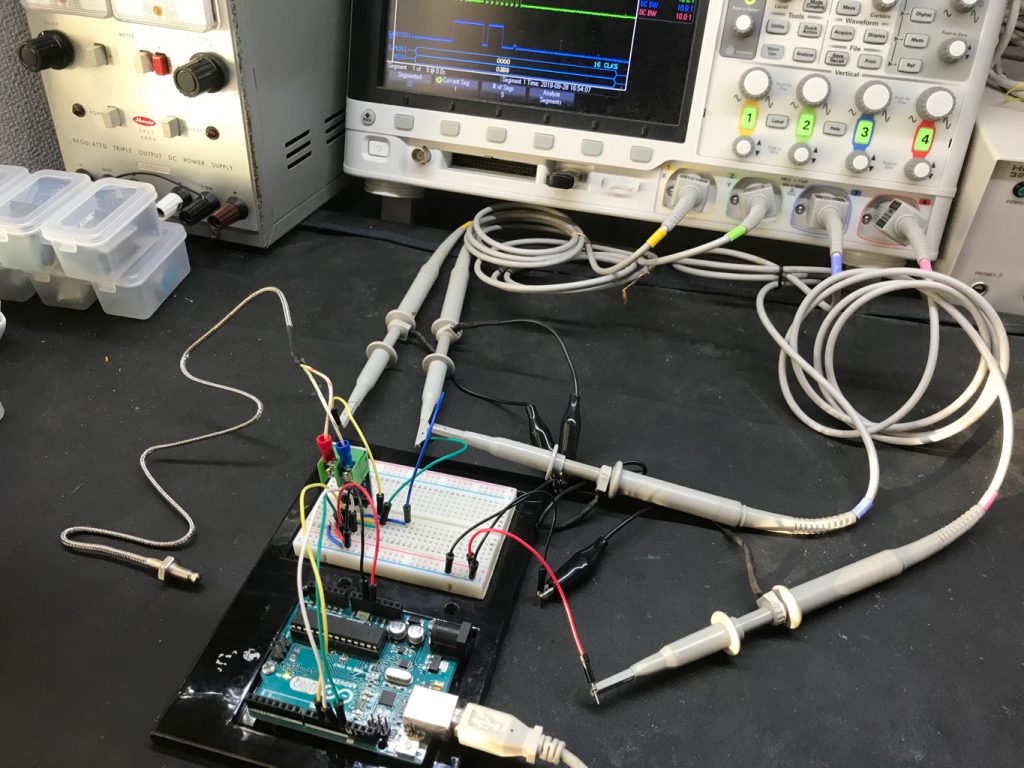

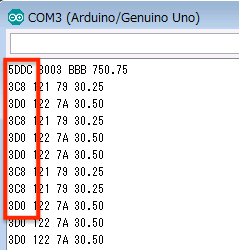

MAX6675(写真1)はSPIインターフェースを持つ、K型熱電対用センサーです。Arduinoを使って評価をしていたのですが(写真2)、COMに表示されるデータのうち、一番目のデータのみあり得ないデータになってしまいました。

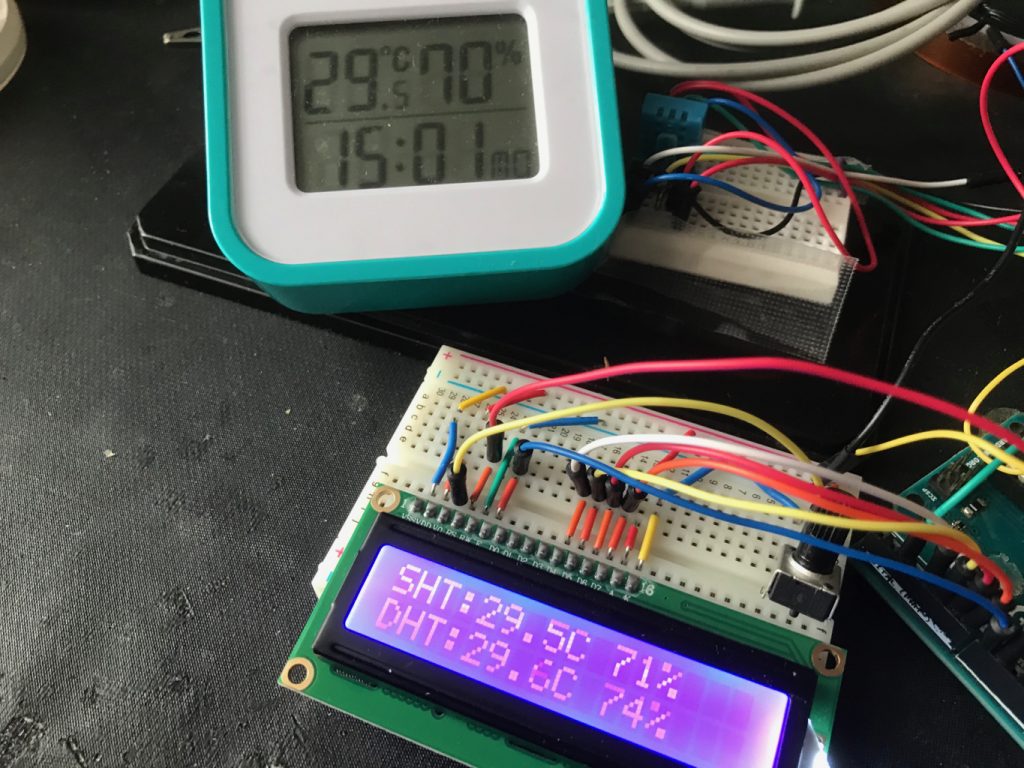

写真2 測定の様子

写真2 測定の様子

SPIインターフェースに流れる波形を確認したいので、

キーサイトテクノロジーのオシロスコープDSOX2014を使った

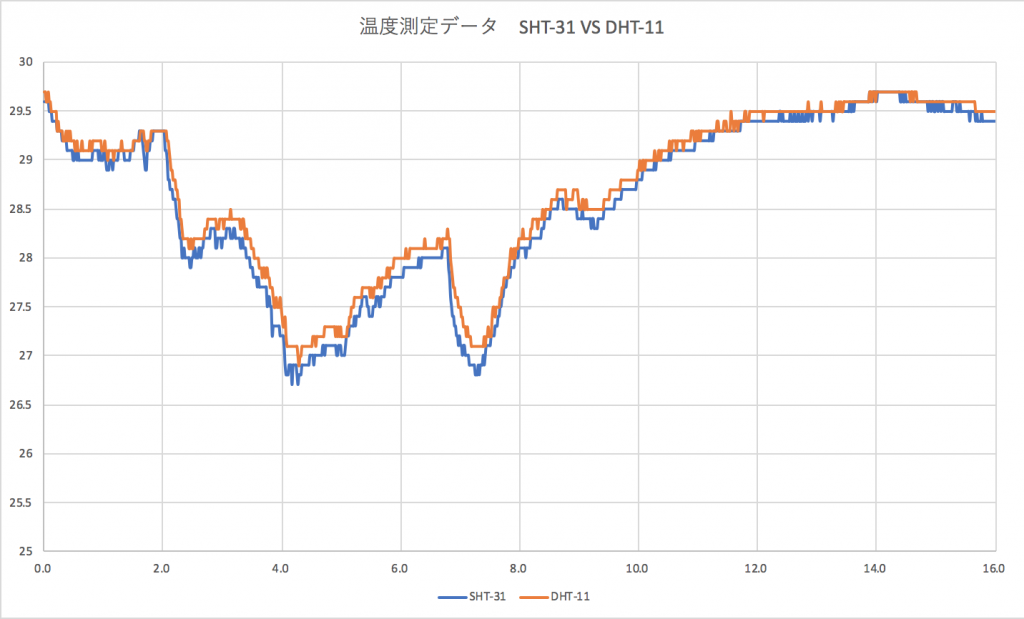

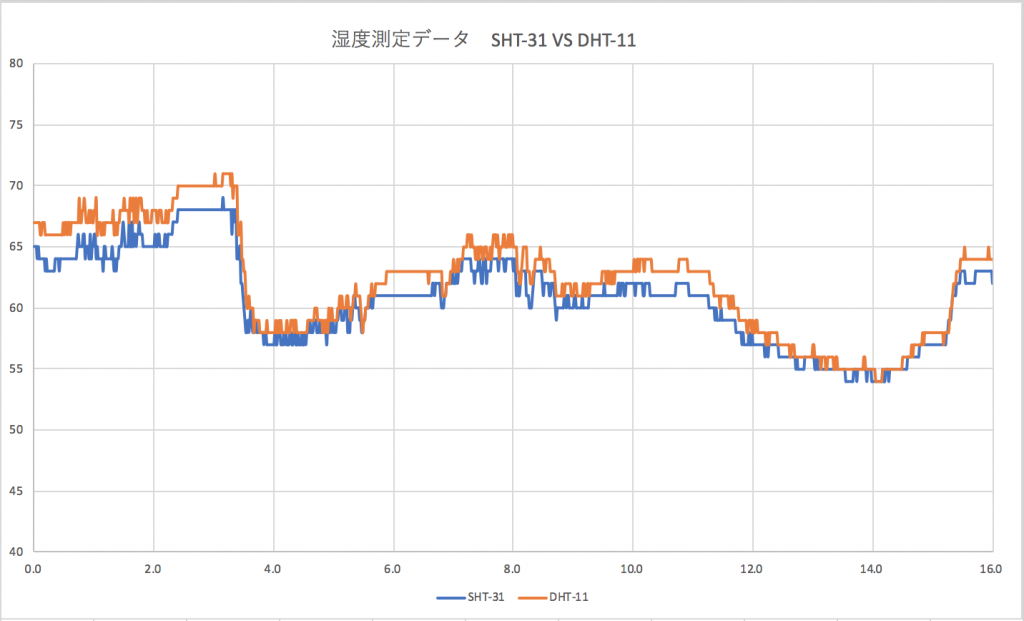

図1 1回目はあり得ないデータが取得されている。2回目以降は問題ない。

図1 1回目はあり得ないデータが取得されている。2回目以降は問題ない。

このエントリでは、なぜ一番目のデータのみ、あり得ないデータが取得されたその理由と対策を備忘録として記載します。